Microchip 25AA640A-I/SN 64K SPI Bus Serial EEPROM: Features and Application Design Considerations

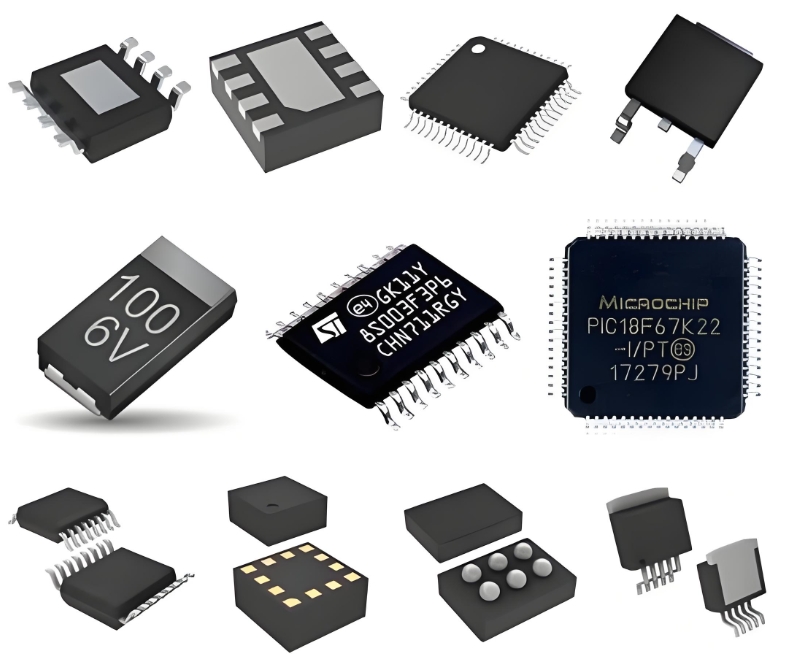

The Microchip 25AA640A-I/SN is a 64-Kbit (8,192 x 8) Serial EEPROM featuring the high-performance SPI serial interface. This device is engineered for a broad range of applications requiring reliable non-volatile memory with low power consumption and a small form factor, making it a cornerstone component in modern embedded systems.

Key Features and Performance Advantages

The 25AA640A-I/SN stands out due to its robust set of features designed for both flexibility and reliability. It supports a high-speed SPI clock frequency of up to 10 MHz, enabling rapid data transfer for time-sensitive operations. Its voltage range of 1.8V to 5.5V allows for seamless integration into both 3.3V and 5V systems, enhancing its versatility across different design platforms.

A critical feature for data integrity is its built-in hardware write-protection via a dedicated `HOLD` pin and a software-protected `WP` pin. This allows sections of the memory array to be locked against inadvertent writes, safeguarding crucial configuration data. Furthermore, the device boasts a high endurance of 1 million erase/write cycles and offers exceptional data retention of over 200 years, ensuring long-term reliability.

The 25AA640A also includes advanced functionality like sequential read capability, which allows the entire memory array to be read with a single command, significantly improving read efficiency. Its low-power consumption in both active and standby modes makes it an ideal choice for battery-powered and portable devices.

Critical Application Design Considerations

Successfully integrating this EEPROM into a design requires careful attention to several key areas:

1. SPI Interface and Signal Integrity: The SPI bus is highly susceptible to noise, especially at high clock speeds. To ensure robust communication, designers must keep SPI trace lengths short, use appropriate pull-up resistors if necessary, and avoid routing these signals near noise sources. Proper grounding and decoupling, with a 0.1 µF ceramic capacitor placed as close as possible to the `VCC` and `GND` pins of the device, are essential for stable operation.

2. Write Cycle Timing and Polling: Unlike reading, writing to the EEPROM is a finite-time process. After issuing a `WREN` (Write Enable) command and a `WRITE` command, the device enters a self-timed write cycle (typically 5 ms max). The system microcontroller must not attempt to read the memory during this period. The most reliable method to check for write completion is to poll the `WIP` (Write-In-Progress) bit in the STATUS register. Attempting to read the array prematurely will yield invalid data.

3. Page Write Limitations: Although the memory supports a 32-byte page write buffer, designers must be cautious not to cross a page boundary during a single write operation. If a sequential write exceeds the end of a page, it will wrap around to the beginning of the same page, overwriting previously written data. Firmware must include logic to manage writes that span multiple pages.

4. Noise Immunity and Power Management: In electrically noisy environments, such as those with motors or switching regulators, the `HOLD` pin can be leveraged to pause an ongoing communication without terminating it, ensuring data is not corrupted by a glitch. Additionally, implementing a clean and stable power supply with sufficient decoupling is non-negotiable for preventing brown-out conditions that could lead to write errors.

5. Handling Sleep/Low-Power Modes: For ultra-low-power applications, placing the EEPROM in deep power-down mode (via the `DPD` command) reduces standby current to nanoamps. However, designers must account for the wake-up time required from this state before the device can respond to subsequent commands.

ICGOOODFIND

The Microchip 25AA640A-I/SN is a highly capable and reliable SPI EEPROM solution. Its combination of high speed, low power, extensive voltage range, and robust data protection features makes it suitable for a vast array of applications, from industrial control and automotive systems to consumer electronics and IoT sensor nodes. Successful implementation hinges on meticulous attention to signal integrity, strict adherence to write cycle timing, and intelligent firmware design to manage its advanced features effectively.

Keywords: SPI Interface, Hardware Write-Protection, Data Retention, Page Write, Low-Power Consumption